Overview

The needs for on-chip passive device and package co-simulation increase dramatically due to IC design trend in reducing the chip size, increasing the signal frequency, and stacking multiple chips in a package, even moving towards CoWOS and 3DIC. IC designers need to take into account the overall EM effects from on-chip passive devices to the package bump as part of circuit design optimization. The mutual coupling between interconnects, bumps, and vias also play an important role to affect the circuit performance. It is desired to have a single EDA platform to serve IC designers for these needs.

The needs for on-chip passive device and package co-simulation increase dramatically due to IC design trend in reducing the chip size, increasing the signal frequency, and stacking multiple chips in a package, even moving towards CoWOS and 3DIC. IC designers need to take into account the overall EM effects from on-chip passive devices to the package bump as part of circuit design optimization. The mutual coupling between interconnects, bumps, and vias also play an important role to affect the circuit performance. It is desired to have a single EDA platform to serve IC designers for these needs.

The application of PeakView LEM has been expanded to package elements and board-level analysis. PeakView offers a convenient integration with chip design tools and package/board design tools, allowing users to skip the tedious configuration of traditional modeling tools and to achieve the truly optimized design by considering the whole physical environment in the critical region. Assisted by the innovative flexibility and solid accuracy of PeakView, designers can quickly assess the on-chip device performance after importing the package elements and PCB structures, which might be provided by other partners, to PeakView. Additionally, users can conduct the EM analysis of selected elements while the trivial periphery structures are automatically neglected.

The remarkably adaptive LEM efficiently handles the mix of on-chip/package/PCB structures such as on-chip inductor, bump, RDL/substrate routing, via, package ball, and PCB routing to generate a overall models that taking into account all the contributors. For example, vias produce discontinuity from the signal transition and significantly affect signal and power integrity in high speed designs. Parasitic capacitance of via can also increase signal rise time. The PeakView high capacity computation engine enlarges the computable dimensions to millimeter scale, but you can still get the most accurate model of the micron level on-chip devices.

Benefits of using PeakView On-Chip Packaging Co-simulation:

- A tool that is easy to setup and requires minimum EM expertise to use

- Optimized to handle special on-chip structures like via array

- Support and services such as design customization are available

- Shorten the design flow and make optimization of the whole design possible

EM Key Challenges: Vertical Inductance

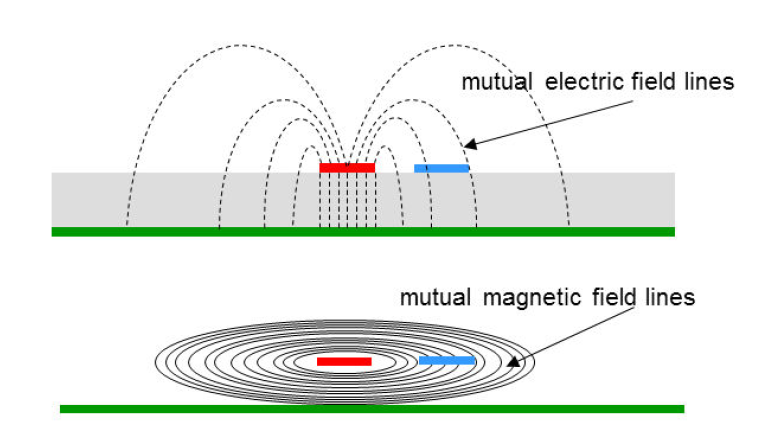

For chip and package EM co-simulation, the vertical current through conductor and vias are important. Vertical inductance is notoriously difficult to capture including vertical inductance of vias, vertical inductance of thick metal, and all mutual coupling among vertical currents. PeakView overcomes this difficulty through rigorous vertical meshing and EM equations.

Bump Issues between IC/PKG and Peakview EM Modeling

While PDK includes layers only up to UBM (Under bump metal) and packaging tools include in PKG/PCB levels, solder ball (Bump) layers are not defined either in PDK or in packaging design tools. Without a special treatment, there is no connection between IC and PKG and vertical current bump effects will be missing.

Peakview has provided IC/PKG EM solution through incremental profile approach. This allows for TSV, UBM, BUMP and packaging layers EM co-sim with IC, and passivation opening and its setup in profile.

Visualization of the IC, Packaging and PCB Layers

PKG/PCB Import and Export Integration

1. Layout to PeakView using Cadence Virtuoso:

PeakView has been well integrated with Cadence Virtuoso. Users just need to click “Layout EM…” to transfer the layout data including pins to PeakView directly.

2. Layout to PeakView using GDS:

Users can easily stream in a GDS file into PeakView as a new cell. The “pin text file” records the name, layer and coordinates of all pins.

3. Layout to Peakview using ODB++:

PeakView supports importing design layouts using Virtuoso, GDS, and ODB++ formats. Users can transfer the layout data including pins to PeakView.

4. PKG/PCB Export ODB++ for 3rd Party EDA Co-simulation:

PeakView supports exporting design layout in ODB++ as well. It can be imported to true 3D EM simulator for system level simulation.

Supporting the IC and CoWoS/3DIC Co-simulation Flow

PeakView’s comprehensive EM simulation capabilities for IC-CoWoS/3DIC designs and IC-packaging co-designs is a significant advancement in meeting the increasing demand for reliable and accurate EM simulations in advanced-node IC designs. With its large-scale 3D EM simulation capabilities, PeakView is able to perform CoWoS and 3DIC EM co-simulations for RF, mmWave, and high-speed analog designs. By leveraging techniques such as special CoWoS profiles, packaging increment profiles, volume meshing, 3D accuracy, and vertical inductance, PeakView is able to achieve high accuracy and solver capacity in large-scale simulations.

PeakView also offers easy setup for computing critical EM isolation and crosstalk between the chip and the interposers, ensuring that designers have a comprehensive understanding of the EM effects on their designs. This is particularly important given the increasing use of TSMC CoWoS and 3DIC technologies in advanced-node IC designs. With its close collaboration with foundries on process and PDK integration, PeakView is well-positioned to address the challenges of comprehensive EM simulations for advanced-node IC designs.

Modeling of the Interposer Structures

To add on, Multi-Sheet Current (MSC) is a unique technique in PeakView that allows efficient simulation of complex multi-layered structures with large numbers of vias and interconnects. It combines full-wave 3D EM solvers with an accurate calculation of the multisheet currents to provide an accurate representation of the vertical currents and mutual coupling effects in the structure. This enables designers to accurately simulate and optimize the performance of their chip-package systems, taking into account the effects of parasitic elements such as inductance and capacitance.

Bumps are modeled as via-bars between the UBM layer and the first RDL layer, while pad shape is usually done as octagons instead of circular ones due to denser meshes involved.

PeakView 3DIC EM Co-Sim Flow:

Layouts are loaded from GDSII files, while PeakView accommodates other formats,such as ODB++, and directly syncs them from Cadence. IC and CoWoS layouts are merged in PeakView to create a combo IC-CoWoS layout.

PeakView’s HCS & Visualization Feature Help Designers to Navigate Through 3DIC Design Challenges

IC, CoWoS and 3DIC EM Co-Sim requires denser meshes on on-chip structures and coarser meshes on CoWoS and 3DIC ones, and it usually leads to large-scale simulation which solves millions of unknowns and hundreds of ports. Visualization of the IC, Packaging and PCB Layers help designers navigate through the 3DIC EM design challenges: