## LORENTZ SOLUTION

# **PeakView Layout EM (LEM)**

## **Overview**

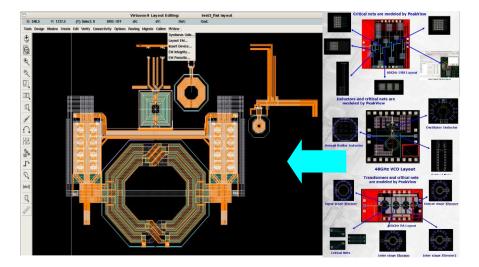

PeakView's LEM<sup>™</sup> is a powerful yet easy to use, 3D EM modeling solution. It can be operated as standalone or from within Virtuoso<sup>®</sup> or Laker<sup>™</sup> design environment with a simple click of button for passive device and interconnect structures to be automatically extracted for a complete 3D electromagnetic analysis. PeakView's high-capacity EM engine supports complex multi-port structures and produce accurate EM models with corresponding views for the selected library.

LEM<sup>™</sup> provides a versatile user interface and enables designers to incrementally adjust the parameters of devices throughout design. Composite layouts with passives, interconnects, DFM structures (e.g. fill) and wafer scale package elements can be EM analyzed together. The state-ofthe-art electromagnetic simulation technology provides the performance, capacity and accuracy for meeting today's most stringent electromagnetic IC design needs.

## **Features**

#### **Advanced EM Modeling**

#### 1. Support for Advanced Processes

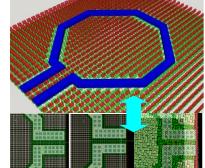

LEM<sup>™</sup> addresses sub-40nm challenges in advanced processes with the PeakView<sup>™</sup> chemical-mechanical polishing (CMP) option. This feature allows

LEM<sup>™</sup> to accurately simulate and model complex metal slotting, striping, and via arrays, aiding time-efficient automated design. It provides comprehensive modeling methods for dummy metal fill with passive devices over all frequency ranges.

PeakView LEM<sup>™</sup>, in conjunction with CMP<sup>™</sup>, provides full support for advanced process node DFM requirements during EM synthesis and Layout EM extraction. Designers are able to define their own metal fill and slotting requirements in the PCircuit parameters. During EM synthesis, these rules are considered and PeakView delivers a DRC clean layout with accurate EM and circuit simulation models.

## **Benefits**

#### Support Advanced Process Nodes & Technologies

support for advanced process nodes from 65nm to 7nm PDKs with the most up-to-date design rules and utilities (i.e. metal-fill). PeakView's iRCX and ITF Parsers simplify importing PDK layer process information into the tool. All process nodes with any metal stack-up are supported in LEM<sup>™</sup>.

#### **Design Flow Support**

IntegrationLEM<sup>™</sup> is seamlessly integrated into the Virtuoso® and Laker<sup>™</sup> layout editors with a bi-directional, lossless data exchange interface. Designers are able utilize the tool in their familiar IC design environment.

# Accuracy, Capacity & Performance

PeakView's patented EM solver combines high accuracy, computational performance and capacity needed to analyze complex layouts with devices, interconnect and PCM interfaces.

#### **Automated Layout Processing**

PeakView<sup>™</sup> automatically processes compound designs and generates corresponding layouts for EM simulation. The layouts are algorithmically verified and modeled; users are not required to make any modification (e.g. simplifying via, metal fill etc.) to their designs. With automated internal layout processing, PeakView<sup>™</sup> LEM generates signoff quality models with no loss in accuracy.

#### 2. Physics-Based Modeling

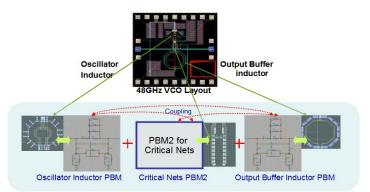

In addition to purely numerical n-port S-parameter models, LEM<sup>™</sup> also provides the option to generate compact RLCK models called Physics-Based Models (PBM) that guarantees passivity and physical realizability. PBM generates EM models as Spectre or HSPICE equivalent sub-circuits for use in transient simulations. PBM models are guaranteed to be convergent and passive over a user selectable frequency range. PBM preserves the DC inductance and resistance, and does not shift the circuit's operating point. In addition, PeakView PBM automatically ensures that the model correctly accounts for white noise content.

Interconnect with irregular or non-uniform structures can also be modeled with 2<sup>nd</sup> generation Physics-based Models (PBM2). PBM2-based LEM is able to convert S-parameter models of arbitrary geometries with high port counts into compact equivalent circuit models that can be used in time-domain circuit simulations. This enables designers to easily perform transient simulations of their designs with EM-level accuracy.

#### 3. Hierarchical EM

PeakView<sup>™</sup> Hierarchical Electromagnetic (HEM) solution is an elegant strategy for reduction of computational complexity to yield a faster simulation time than a flatmode solver. The HEM engine uses a divide and conquer algorithm to partition a large problem into smaller counterparts. With the aid of parallel processing, the smaller geometries are first solved quickly. The partial solutions are then iteratively combined into a final solution of the original problem by computing the global coupling effects among the sub-components.

#### **Tool Integration**

#### 1. Process Corner and Temperature Coefficient Modeling

PeakView<sup>™</sup> generates Sparameter and lumped models that account for process corner and temperature sweeps. Foundries provide several types of technology files in terms of Rbest, Rworst etc., that reflects process variations.

Temperature coefficients of materials are also obtained

Weta stacking profile

Comer/Temperature Sweep in PeakView

ADE-XL Corner/Temp Sweep

With a stacking profile

Image: Additional additinadditionadditadditionadditional additional additadditio

from technology files. PeakView<sup>™</sup> generated corner based model files accounting for process corners and temperature coefficient analysis and can be synced to the design library. The models can be utilized within popular simulation environments such as ADE-XL.

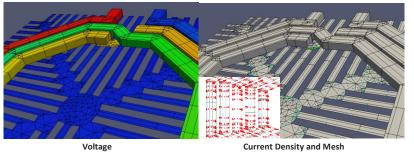

#### 2. Visualization

PeakView LEM's visualization system expedites debugging of device design by showing the EM mesh, voltages, currents and charge distribution. Inaccuracies in the structures are apparent early and can be fixed preemptively in the design phase. The built-in visualization window provides for better understanding of skin effects and capacitive coupling, image currents at various frequencies. The chart window plots pre-defined and user-defined quantities of interest from EM simulation results.

Voltage and charge visualization LEM simulations are shown in the above figure.

#### 3. Support Backward Compatibility with Legacy Layouts

PeakView LEM<sup>™</sup> supports legacy designs containing devices that are not synthesized with Peakview<sup>™</sup> or that were created with Virtuoso<sup>®</sup> prior to use of PeakView<sup>™</sup>. After EM extraction with LEM<sup>™</sup>, the S-parameter and circuit models of each device are generated. PeakView<sup>™</sup> prepares models for Cadence Spectre RF and HSPICE simulations.

#### **High-Performance Features**

#### 1. Customized Accuracy Types

In addition to pre-configured EM simulation types, PeakView<sup>™</sup> has implemented Pre-Customized Accuracy Types to enhance the flexibility of accuracy settings and to configure layout processing and EM simulation options. By composing a configuration file, users can easily tune the tool such that the entire EM simulation process is optimized for special test cases. This is particularly useful for scenarios

|                                                                                    | Interconnect: fastest simulation for interconnect and simple structure<br>onChipQuick: fast and quick estimate<br>onChipNormal: medium accuracy to balance speed/accuracy trade-off<br>onChipConservative: high accuracy for sign-off quality |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Circuit Parameter Editor                                                           | onChipMMWave: high accuracy for high frequency designs<br>RDL: large dimension/diameter/path width                                                                                                                                            |

| Circuit Name [IND]<br>EM Simulation Type onChipNormal :<br>Terminal Order pl p2 p3 |                                                                                                                                                                                                                                               |

| Apply Advance Scancel                                                              |                                                                                                                                                                                                                                               |

where concurrent simulation for structures of varying scales is required.

#### 2. Multi-core Processing and Distributed Computing

To maximize utilization of computing resources, LEM<sup>™</sup> takes advantage of PeakView's multi-core processing capability. Design jobs can be run on compute farms consisting of multi-core machines, as well as on standalone platforms with multi-processor hardware to achieve maximum efficiency of computing resources. PeakView provides different distributed computing modes to concurrently accelerate the EM modeling. Users can specify different frequency points to be simulated on different machines in a compute farm.

#### 3. Hybrid Matrix Decomposition Technology

PeakView<sup>™</sup> has developed a hybrid matrix decomposition technology to achieve rapid solutions for both DC and EM simulation. A set of advanced mathematical methods which combines the advantageous aspects of sparse matrix and dense matrix solution technologies has been implemented in the engine. The overall simulation time is now greatly minimized with the new developments in matrix decomposition methodology.

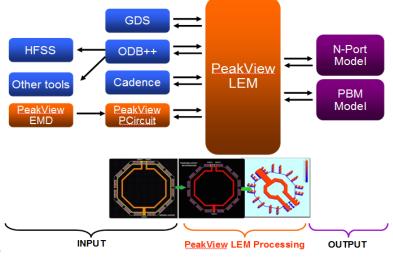

### **LEM™ Flow**

The PeakView LEM<sup>™</sup> flow accommodates three different modeling approaches frequently used by designers. For Layout EM analysis users can: **1.** launch LEM<sup>™</sup> from within their Virtuoso<sup>®</sup> environment and export their layouts to PeakView<sup>™</sup>, **2.** Import a GDSII format layout file into PeakView<sup>™</sup> or, **3.** Synthesize a layout in PeakView<sup>™</sup> using PCircuits. Design layouts that contain compound structures of varying scales (on-chip devices, large RDL lines, PCBs, planar package elements) and contours (polygons of any angles, circular via holes, curved paths) are accurately processed by LEM<sup>™</sup>. LEM<sup>™</sup> generates a corresponding layout in the

PeakView<sup>™</sup> GUI. PeakView's high precision EM engine is then used to electromagnetically analyze the layout and create relevant views corresponding to the EM models. Generated views are then synced to the Virtuoso<sup>®</sup> Library to be used for SPICE simulation.

## **Applications**

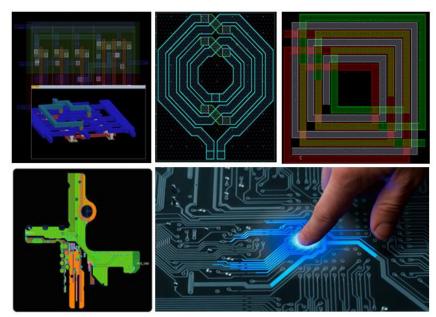

LEM<sup>™</sup> is useful for a wide variety of applications in semiconductor design. LEM, based on PeakView<sup>™</sup> high precision, 3D EM solver, performs accurate signal integrity analysis on complex layouts consisting of a broad class of elements.

LEM<sup>™</sup> efficiently characterizes broadband (e.g. clock-lines), as well as narrowband (e.g. LNAs) applications, from DC to the sub-THz spectrum. Applications include, but are not limited to:

#### **Passive Devices**

Inductors, MOM cap, MIM cap, baluns, transformers and commonly used device topologies and associated metal fill, guard-rings, patterned ground shields, etc.

#### Interconnect

Microstrip lines, co-planar waveguide (CPW) lines, T and X junctions and other planar transmission media or signal routing

#### **DFM Structures**

Metal fill, wide-metal slotting, striping in advanced process nodes (20nm and beyond)

#### **Board-level Analysis**

PCB coupling effects e.g. sensor placement in board-level analysis, feedback impedance return path via ground plane

#### Wafer-Scale Package Elements

Coupling between planar wafer-scale package elements and on-chip passives

## **Silicon Data Correlation**

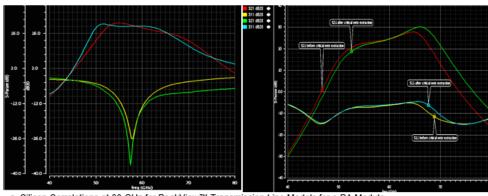

PeakView LEM<sup>™</sup> simplifies the process of complex system-level EM design, and comes close to unique sign-off quality that is bench-marked with measurements. Our products are seamlessly integrated into the IC design environment to support the advanced process nodes, thereby greatly facilitating the key steps for EM design. PeakView<sup>™</sup> EM modeling solutions at 60 GHz and beyond continue to demonstrate excellent correlation to silicon data. Our EM design flows have been demonstrated in TSMC RF Reference Design Kits and test-keys, simulation and measurement results are matched from 40 GHz to 80 GHz.

a. Silicon Correlations at 60 GHz for PeakView<sup>™</sup> Transmission Line Models for a PA Module b. closely matched circuit simulation and silicon measurements for a 60GHz low-noise amplifier (LNA) using PeakView<sup>™</sup> transmission line and inductor models.

Silicon correlation for PA and LNA designs at 60 GHz using PeakView<sup>™</sup> Transmission Line Models for TSMC 65nm process is shown below. Then at TSMC 20nm process, PeakView<sup>™</sup> simulations of inductors with a variety of metal fill shapes and densities were compared to measurements. The result indicated a close match of silicon measurement for bottom plate capacitance when PeakView CMP was used for metal fill modeling.

#### Standard Format Support LEM Setup

- iRCX format technology file from TSMC

- ITF format technology file from foundries

#### LEM Input

- Virtuoso<sup>®</sup> or Laker<sup>™</sup> layout with pins

- GDSII Layout

- PCircuit

#### **LEM Output**

- n-port, Physics-Based EM models.

- Model views added to Cadence<sup>®</sup> Library.

#### Platform

Linux 64-bit, i.e. Red Hat and SUSE LSF/NC-based computing farm.